G-COE PICE International Symposium and IEEE EDS Minicolloquim on Advanced Hybrid Nano Devices: Prospects by World's Leading Scinetists Tokyo Tech., October 4 and 5, 2011

# Challenges of Heterogeneous Integration on CMOS

## Kazuya Masu ICE cube Center Tokyo Institute of Technology http://masu-www.pi.titech.ac.jp

ΤΟΚΥΟ ΤΕΕΗ

**Pursuing Excellence**

1. Introduction Why RF CMOS?

- 2. Our RF CMOS development

- Why do we expect heterogeneous integration on CMOS ?

- 3. Our approach to heterogeneous integration: Novel wafer shuttle technique.

Pursuina Excellence

4. Summary

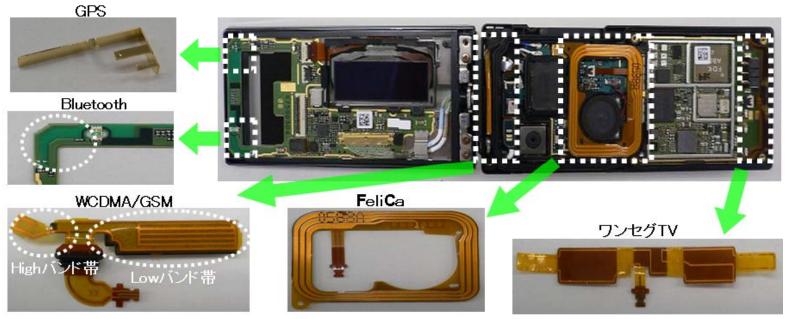

## **Recent mobile phone**

ΤΟΚ

D

**Pursuing Excellence**

#### Freq and wavelength

Courtesy of Hideyuki Saso, Vice President, Fujitsu

## Mobile phone

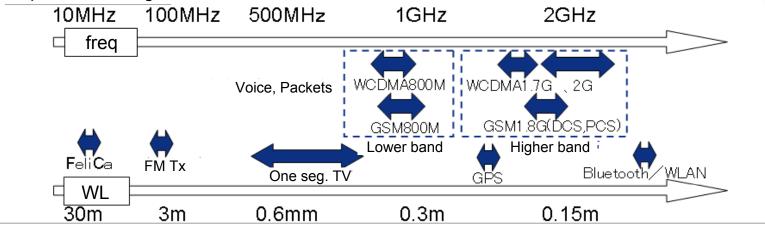

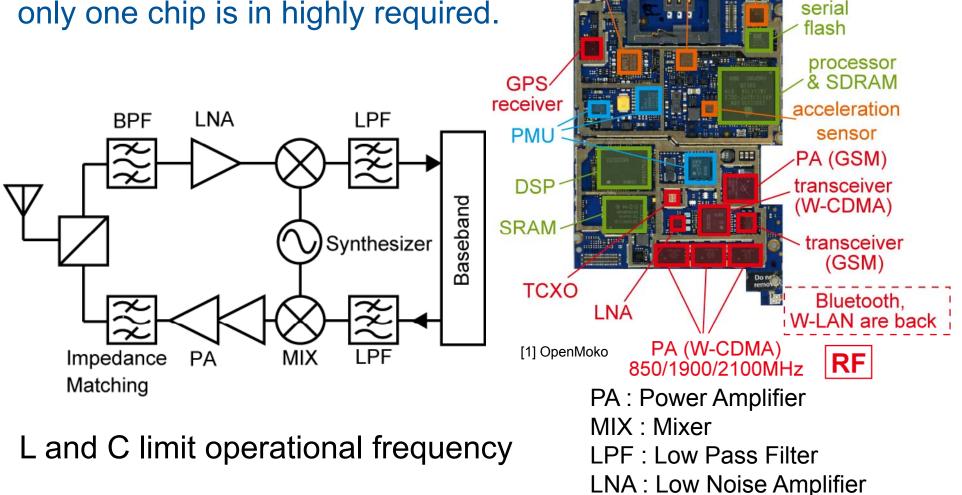

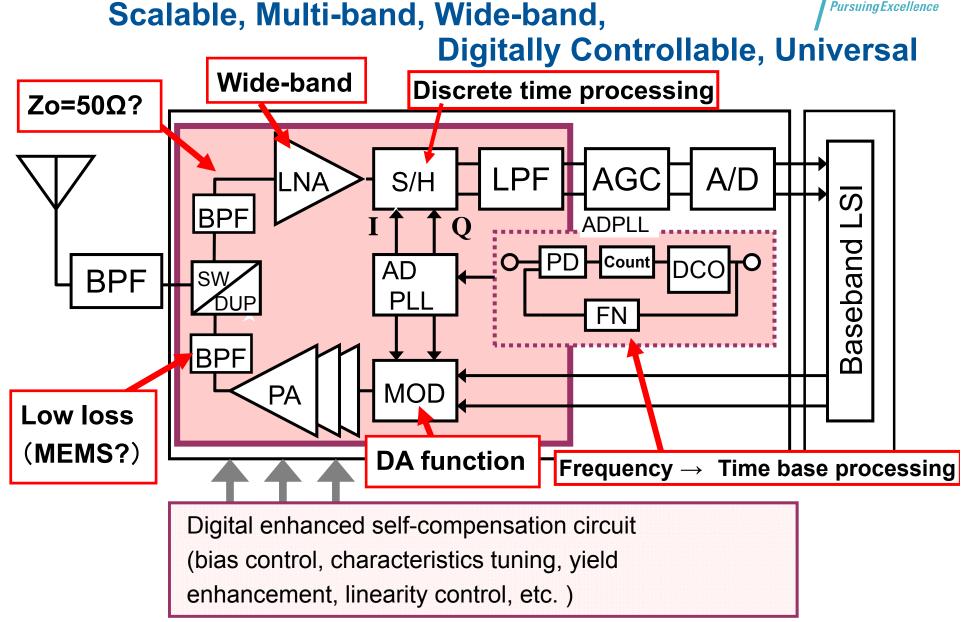

Wideband RF frontend that covers multiple wireless applications with only one chip is in highly required.

ΤΟΚ

display

interface

touchscreen controller

audio

codec

Pursuing Excellence

Digital

## Mutiband/multimode transceiver

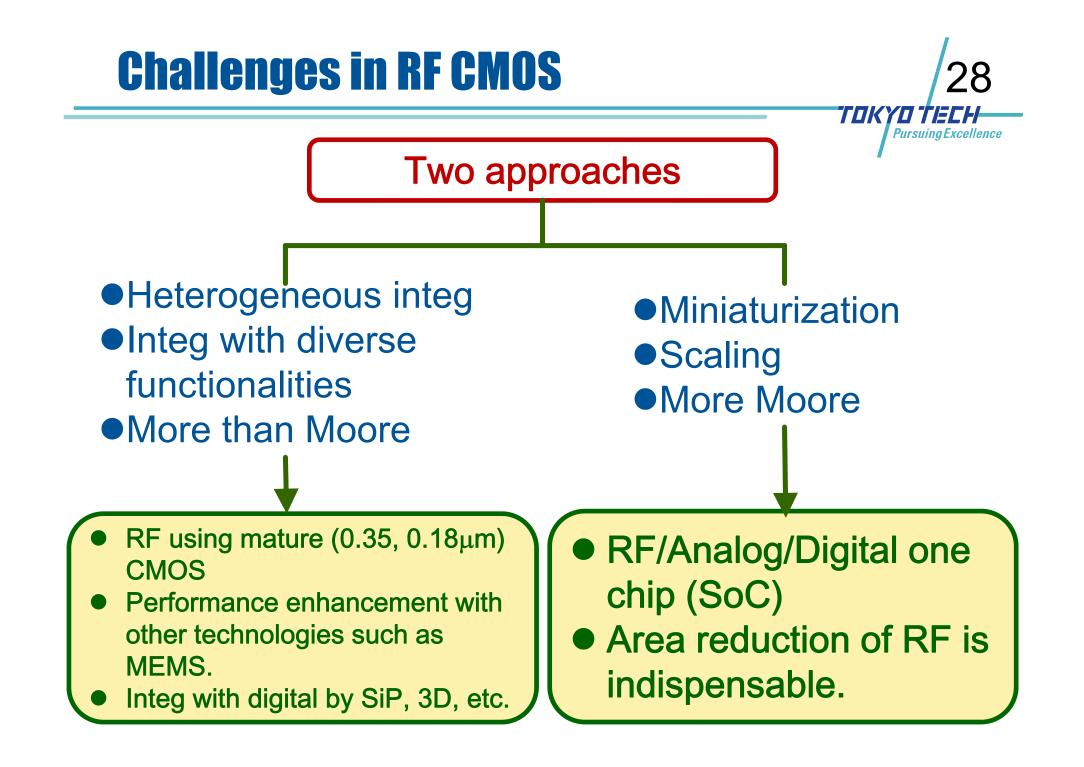

#### TOKYO TIECH Pursuing Excellence

**One terminal**

5

### Many wireless standards (400MHz – 6GHz)

- Mobile phone 800MHz, 1.5GHz, 1.9GHz, 2GHz (+700MHz, 900MHz, 1.7GHz for the new system) (+800MHz, 900MHz, 1.8GHz, 1.9GHz for GSM)

- WLAN 802.11b/g, Bluetooth 2.4GHz

- WLAN 802.11a/n 4.9GHz 5.875GHz

- GPS 1.2GHz/1.5GHz

- DTV 440MHz 770MHz

#### • User's viewpoint

User wants to connect network whenever, wherever, whomever, and whatever.

#### System viewpoint

- Improvement of frequency usage efficiency

- Multiband/multimode wireless communication is indispensable.

Year

## **Miniaturization and Diversification**

Pursuina Excellence More than Moore: Diversification Sensors Analog/RF Passives **Biochips** Power Actuators Baseline CMOS: CPU, Memory, Logic More Moore: Miniaturization 130nm Interacting with people and environment Non-digital content Combining Soc and Sip. Higher Value Systems 90nm 65nm Information Processing 45nm Digital content 32nm System-on-chip (SoC) 22nm 16 nm Beyond CMOS

ΤΟΚΥΟ ΤΕΕΗ

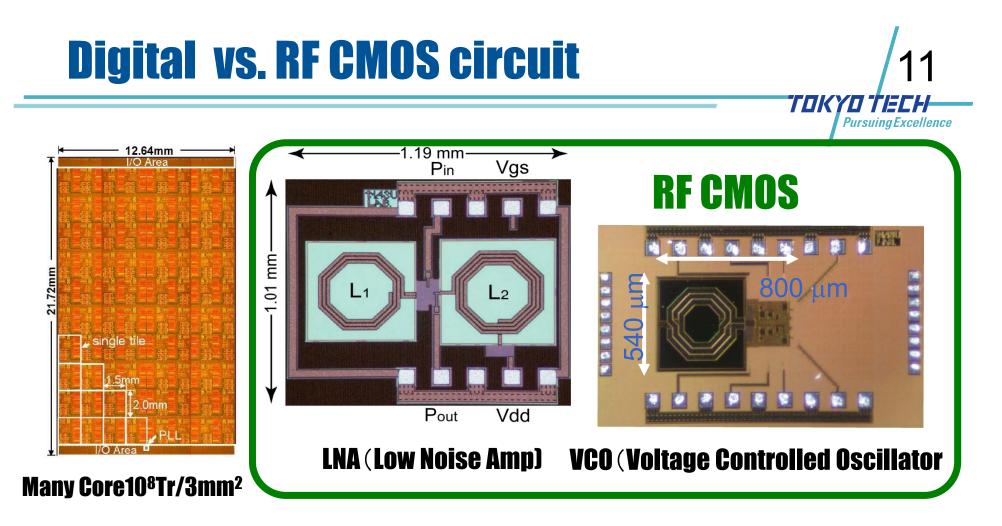

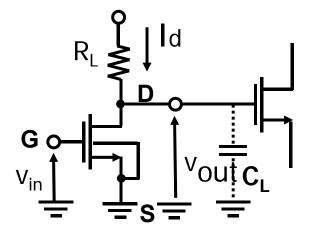

## **Digital vs. Analog/RC LSI**

TOKYO TIECH Pursuing Excellence

• What is difference?

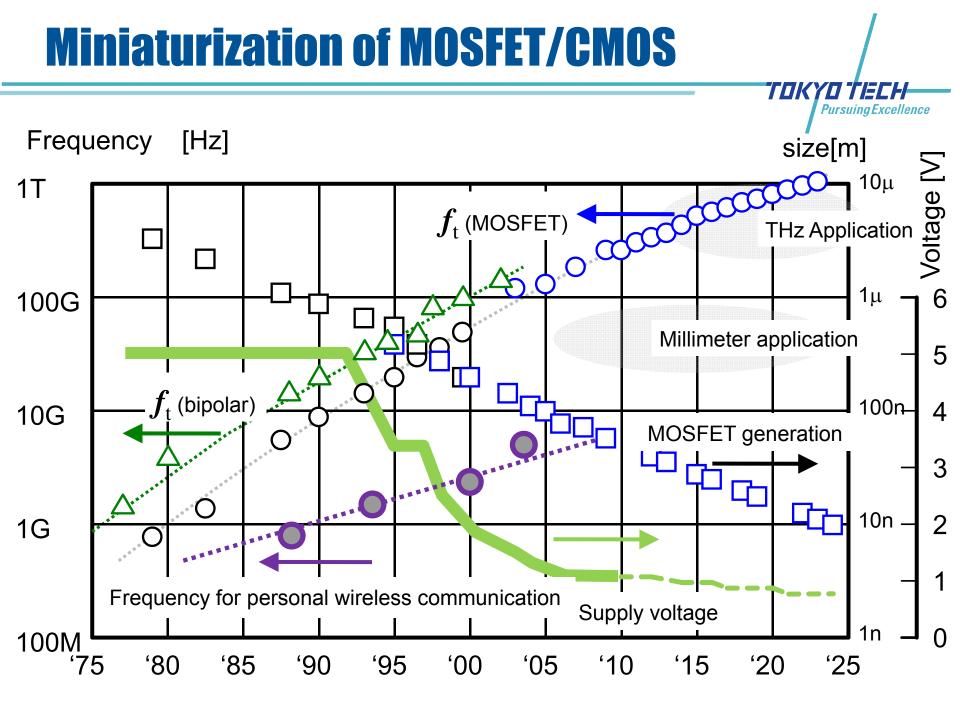

## • CMOS device miniaturization has brought

- High-speed/high-frequency,

- Low consumption power, and

- Chip area reduction.

- Chip area reduction is directly related to lowering cost.

- If there is not area reduction (= cost reduction), miniaturization is meaningless.

- Area reduction of circuit using miniaturized devices is essential!

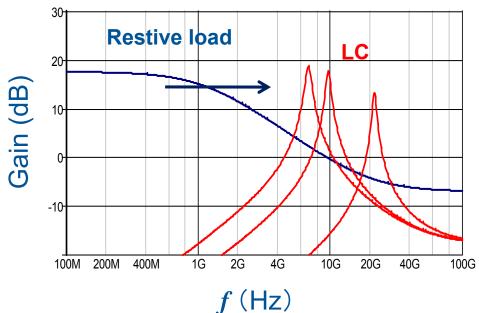

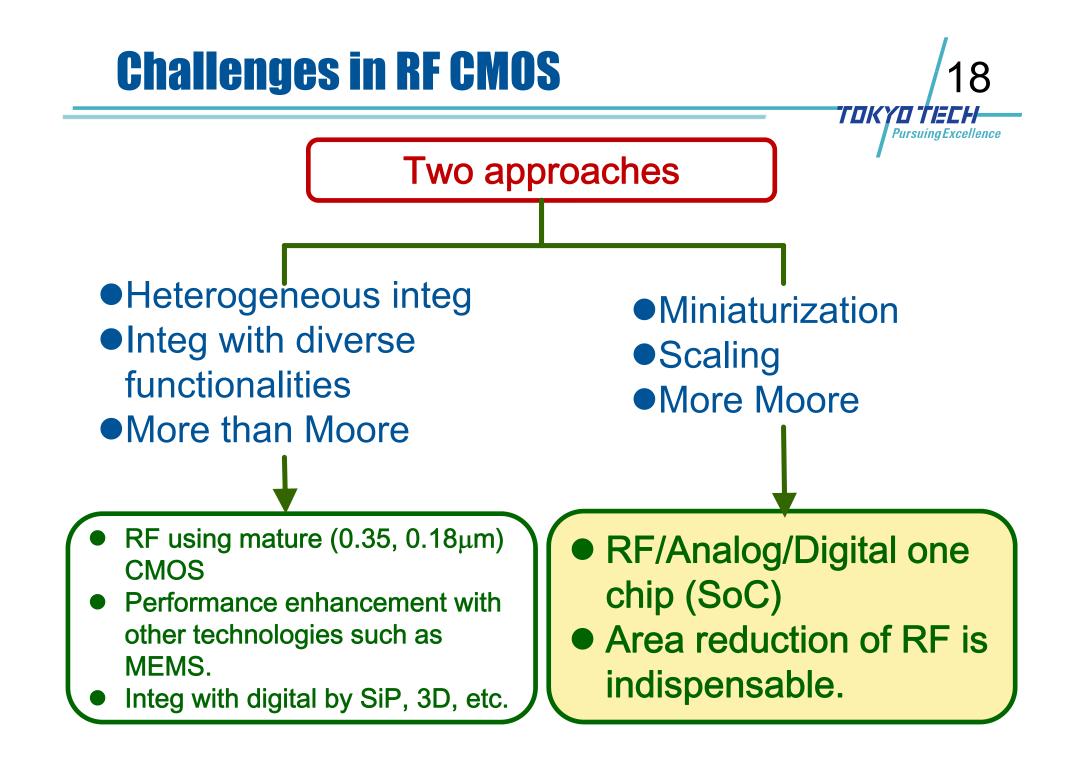

## **RF CMOS**

TOKYO TIECH Pursuing Excellence

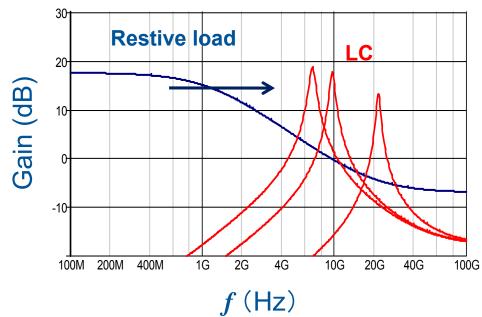

**Restive load**

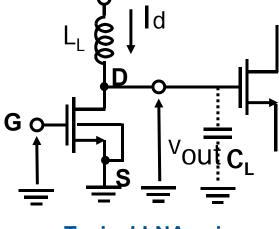

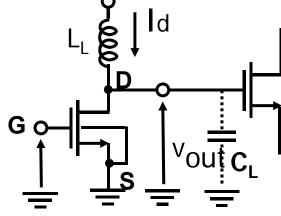

Typical LNA using LC resonance

- Gain of R-load LNA is degraded at high freq because of RC component.

- LNA has sufficient gain at high freq using LC resonance.

- Area reduction is essential in CMOS scaling. Passive devices such as inductor, resistor (including wire) and capacitors consume large area. CMOS devices are miniaturized, however the passives are not miniaturized!

- Challenge of analog/RF circuit design is to reduce the area penalty of passives; ideally elimination of passives.

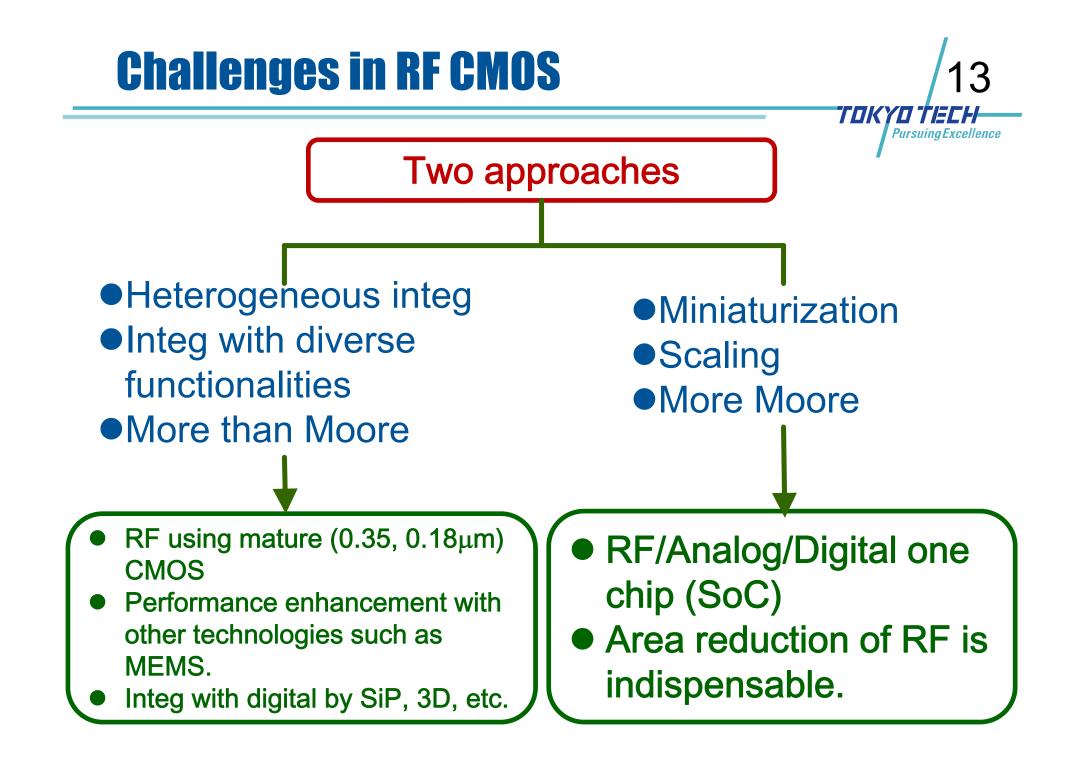

## • RF CMOS has sufficiently high $f_t$ and $f_{max}$

- No need of scaled MOS. 0.18μm/0.13μm CMOS is enough for GHz application.

- Requirement of monolithic integration digital modulation/demodulation and analog/RF signal processing. Passives such as inductor prevent the chip area from reduction.

- Designers design CMOS circuit using PDK (Process Design Kit) supplied from foundry.

- Foundry fabricates CMOS circuit. Designer receive CMOS chip.

- Designers evaluates CMOS circuits.

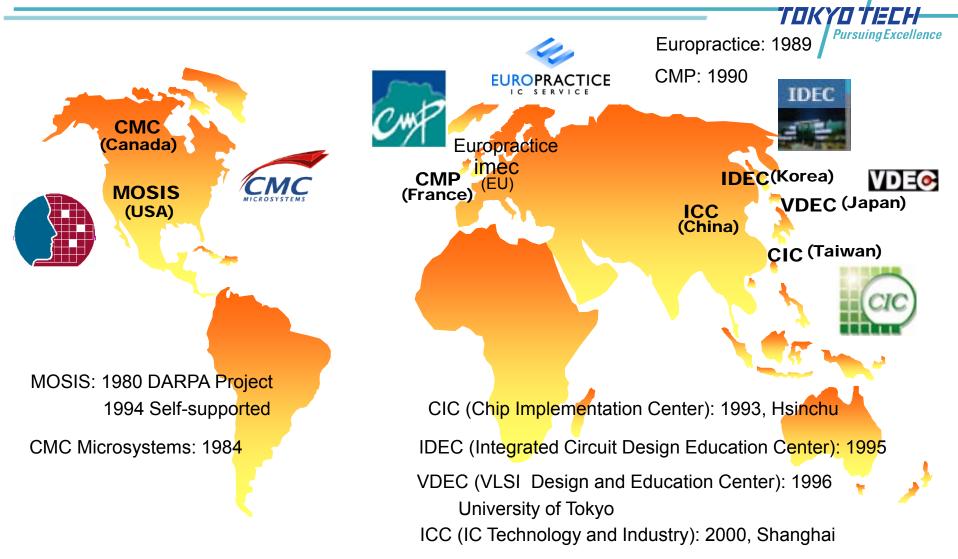

## **Worldwide Service Institutes**

**Major IC Design and Chip Implementation Service Institutes**

## **Worldwide Service Organizations**

|                                            |              |             |        |             |            | <u>, , , , , , , , , , , , , , , , , , , </u> | OTIECH     |

|--------------------------------------------|--------------|-------------|--------|-------------|------------|-----------------------------------------------|------------|

| Country                                    | USA          | Canada      | France | Japan       | China      | Korea                                         | Taiwan     |

| Institutes                                 | MOSIS        | СМС         | CMP    | VDEC        | ICC        | IDEC                                          | CIC        |

| Established                                | 1980<br>1994 | 1984        | 1990   | 1996        | 2000       | 1995                                          | 1993       |

| EDA Tool<br>Vendors                        | x            | NA          | 7      | 9           | 5          | 16                                            | 17         |

| Fabricated<br>Chips (#)                    | NA           | 380         | 391    | 254         | 120+176    | 250                                           | 1621       |

| <b>Processes</b><br><b>Provided</b><br>(#) | 26           | 6           | 15     | 8           | 15         | 8                                             | 14         |

| Advanced<br>Process                        | 40nm         | <b>65nm</b> | 40nm   | <b>40nm</b> | 90nm       | 40nm                                          | 40nm       |

| Packaging                                  | $\bigcirc$   | 0           | Ô      | 0           | $\bigcirc$ | 0                                             | $\bigcirc$ |

| Testing                                    | X            | 0           | X      | 0           | $\bigcirc$ | 0                                             | Ô          |

| Training<br>Coursed                        | X            | NA          | х      | 0           | NA         | Ø                                             | $\bigcirc$ |

Remark: O: Fair Service; O: Excellent Service; X: No Service.

Source: 2009 CMP Annual Report

## 1. Introduction

## 2. Our RF CMOS development

- Why do we expect heterogeneous integration on CMOS ?

- 3. Our approach to heterogeneous integration: Novel wafer shuttle technique.

- 4. Summary

## **RF CMOS**

Gain of R-load LNA is degraded at high freq because of RC component.

G

V<sub>in</sub>

ΤΟΚΥΟ

Pursuing Excellence

IC

D

<del>≡</del>s <del>≛</del>out

- LNA has sufficient gain at high freq using LC resonance.

- Our approach: CMOSinverter base circuit components.

20 TOKYOTIECH Pursuing Excellence

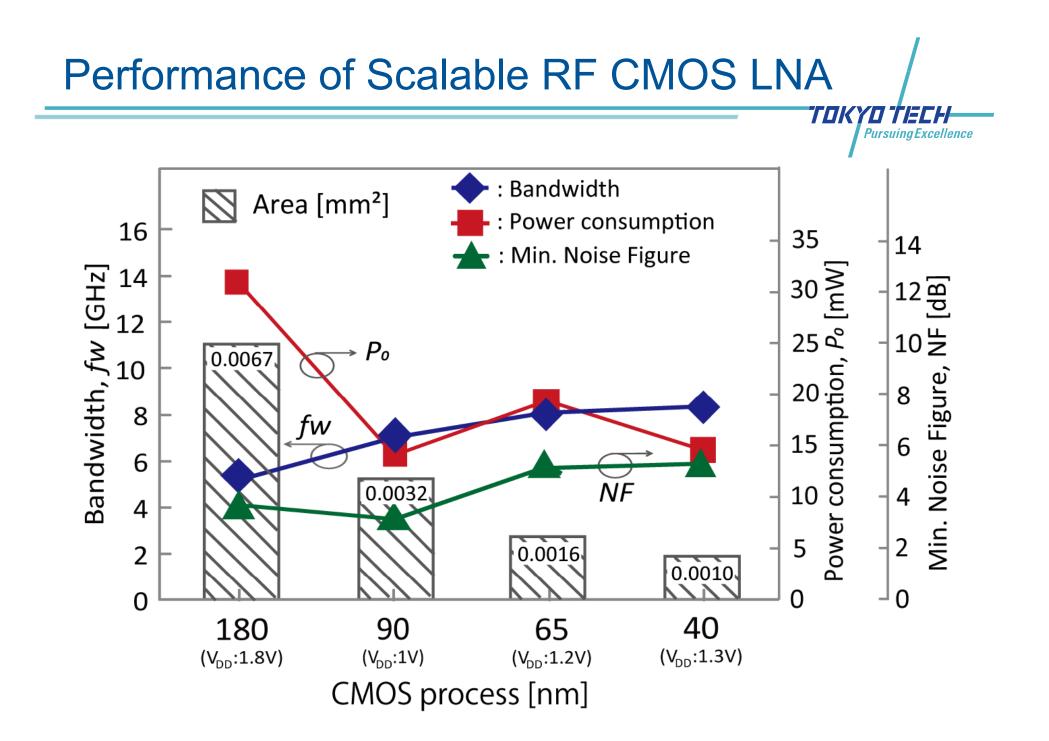

# Our recent work of scalable RF CMOS in 2008-2020

Pursuing Excellence

ΤΟ

|   |                        | PursuinaExcel                                                                                                                                                        |  |

|---|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|   | Scalability            | <ul> <li>Discussion of scalability of the conventional<br/>topology</li> </ul>                                                                                       |  |

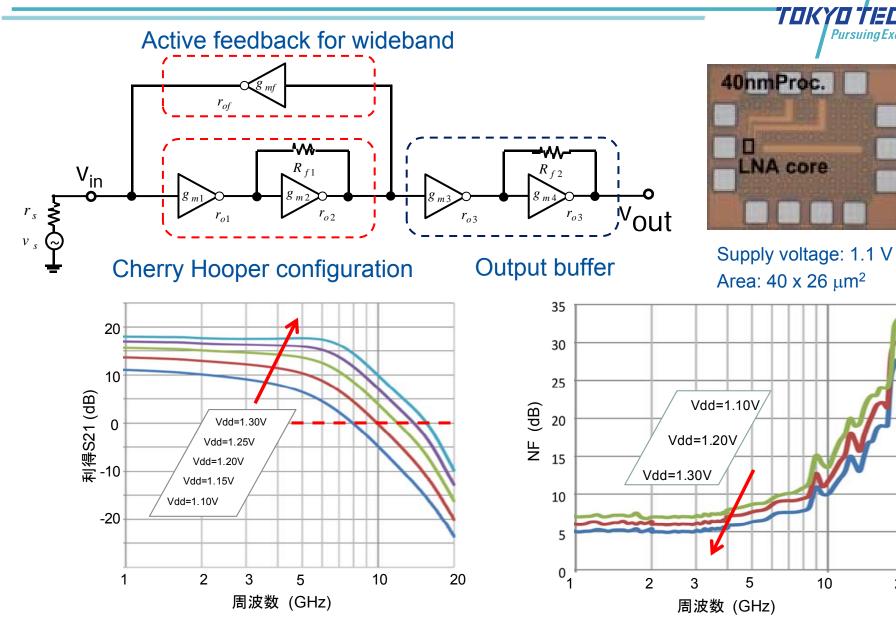

| 1 | LNA                    | <ul> <li>Wideband using Cherry-Hooper &amp; active feed-back</li> </ul>                                                                                              |  |

| 2 | LNA+VGA                | <ul> <li>High-gain LNA+VGA by multi-stage inverter</li> <li>Gain control using MOS-SW</li> </ul>                                                                     |  |

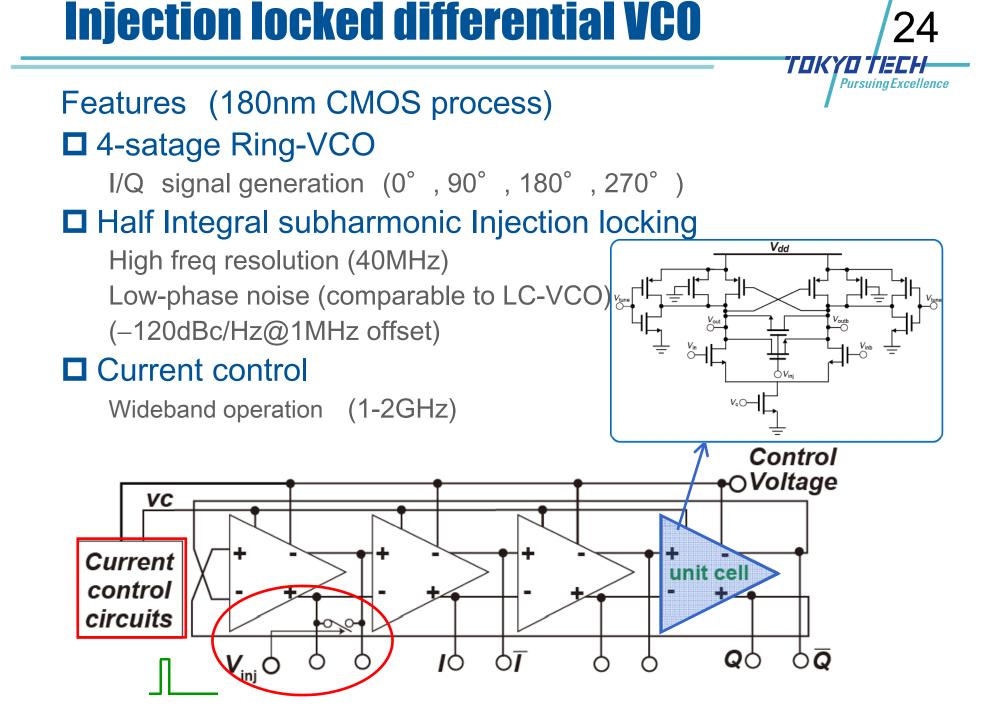

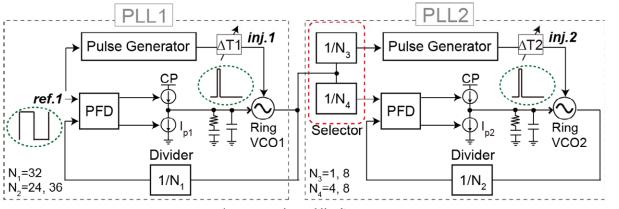

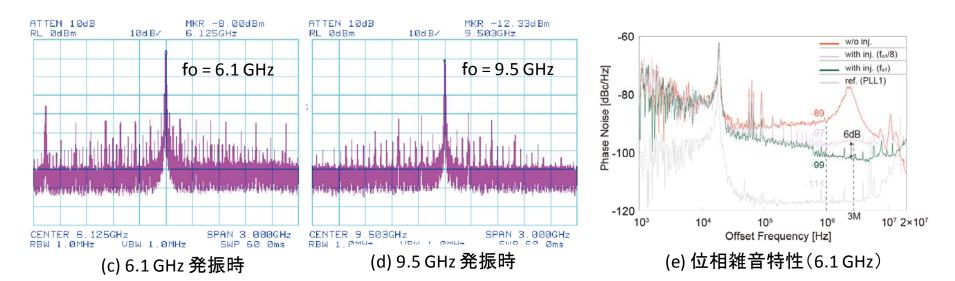

| 3 | Ring-VCO               | <ul> <li>Low phase technique using Injection-lock and<br/>latched inverter</li> </ul>                                                                                |  |

| 4 | PLL using ring-<br>VCO | <ul> <li>Freq synthesizer using PLL combination</li> </ul>                                                                                                           |  |

| 5 | PA                     | <ul> <li>Stacked CMOS for high-power output</li> </ul>                                                                                                               |  |

| 6 | RF modulation<br>block | <ul> <li>RF signal generation using time-to-analog<br/>conversion</li> <li>QPSK signal generation using phase selection and<br/>injection lock techniques</li> </ul> |  |

| 7 | RF demodulation block  | <ul> <li>Passive mixer (on going)</li> </ul>                                                                                                                         |  |

| 8 | Power supply           | ●On-chip LDO                                                                                                                                                         |  |

## **Inverter base LNA**

ΤΟΚΥΟΤΕ Pursuing Excellence

10

20

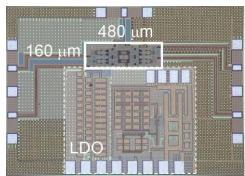

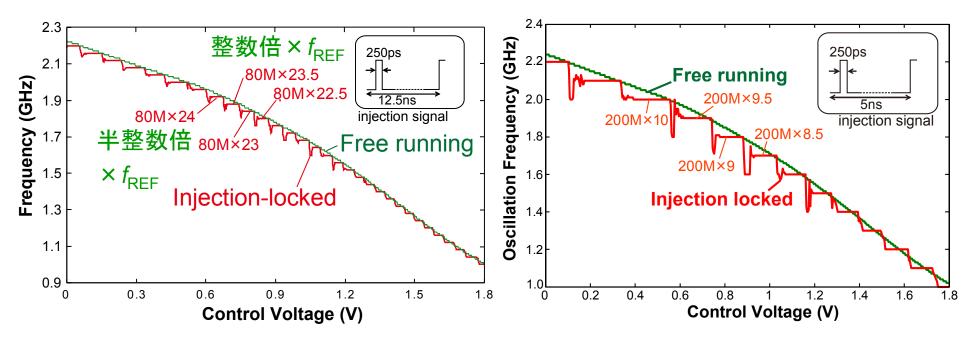

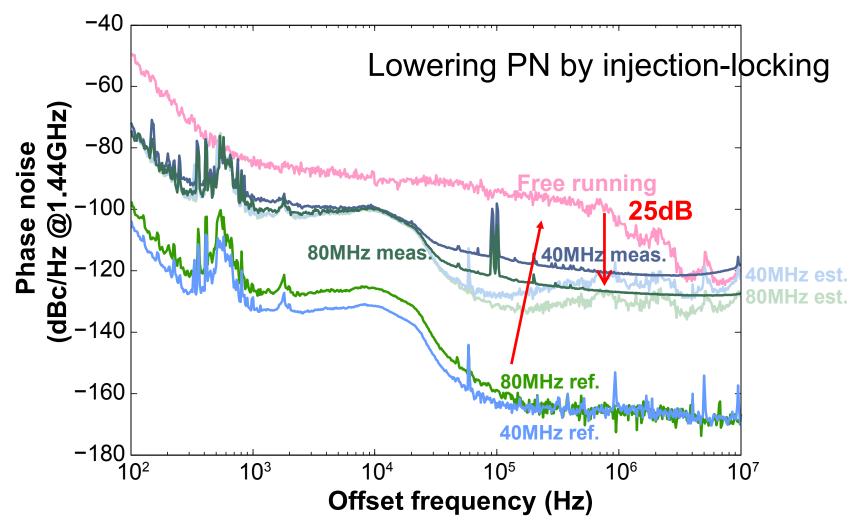

# **Injection lock performance of D-VCO**

#### Chip photo

#### □ Ring-VCO performance

Osc freq (free running):1.0G — 2.2G Power: less than 62mW Phase noise@1MHz offset :-102dBc/Hz @1.44GHz

#### □ Freq performance (ref:80MHz)

#### **Ref: 200MHz**

25

**Pursuing Excellence**

ΤΟΚΥΟ

# Phase noise of injection locked D-VCO

#### □ PN@1MHz offset@1.44GHz

-121dBc/Hz ( input pulse width:250ps 40MHz ): 20MHz resolution

-127dBc/Hz (input pulse width: 250ps 80MHz): 40MHz resolution

## **PLL using ring-VCO**

27 TOKYOTIECH PursuingExcellence

#### PLL using injection-locked ring-VCO

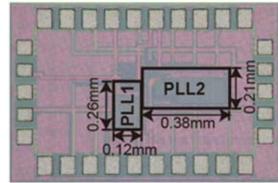

(a) 2ステージPLL回路の構成

(b) 90nmCMOSによる試作チップ

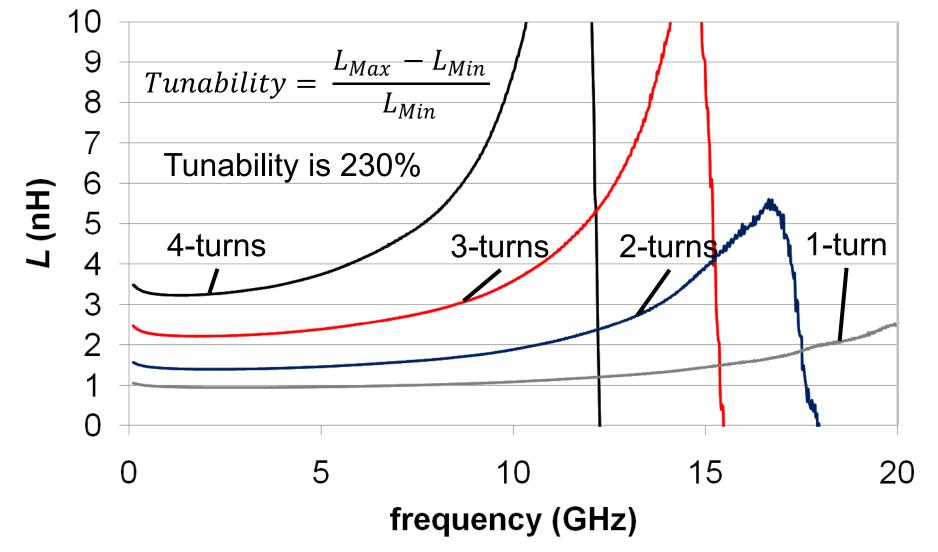

## **Purpose**

29 TOKYOTIECH Pursuing Excellence

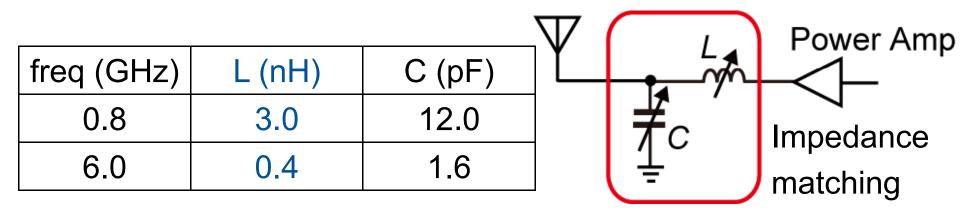

$Z_{out} = 5\Omega$  of PA matching with 50 $\Omega$  of antenna required L and C tuning range at 0.8~6GHz

Purpose: Variable inductor for wideband RF-frontend

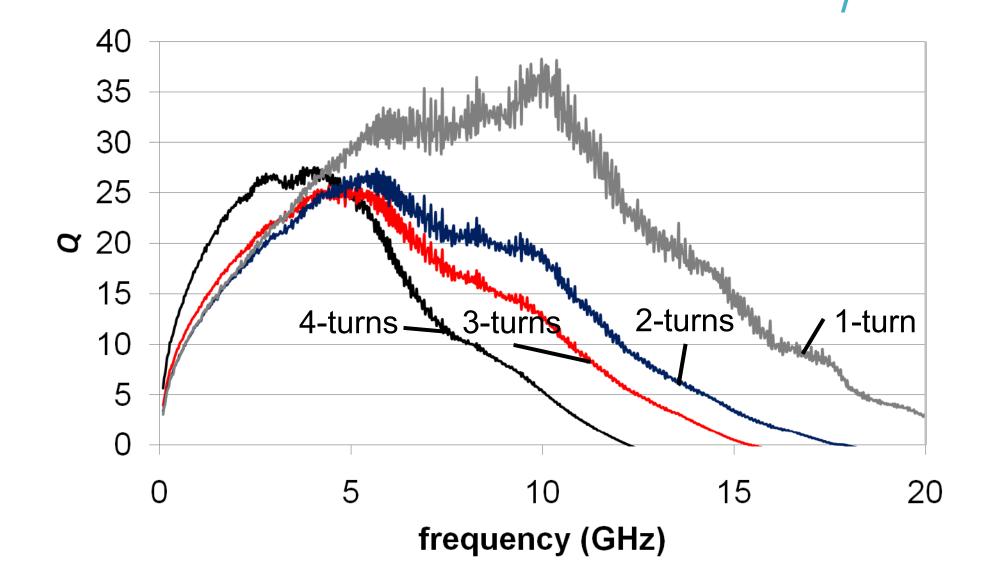

Variable inductor requirements

- •Wide inductance tunable range for wideband operation

- High Q factor to reduce loss

- High self resonant frequency for higher available frequency

####

•Controlling inductance with N switches

- •Decreasing inductance by switching on

- •Switch type variable inductor can easily improve tunability

- •High resolution with fewer switches eg) 8 value with 3 switches

CMOS process can realize this but loss is large

Switches and inductors with lower loss can be achieved by using  $\underline{\mathsf{MEMS}}$

Thick metal and movable structure

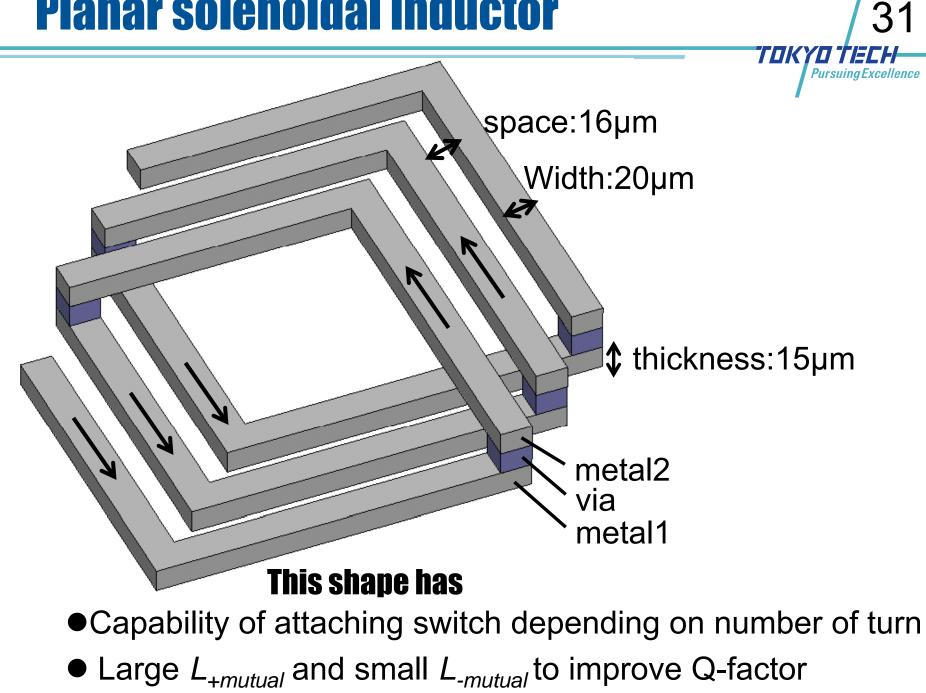

## **Planar solenoidal inductor**

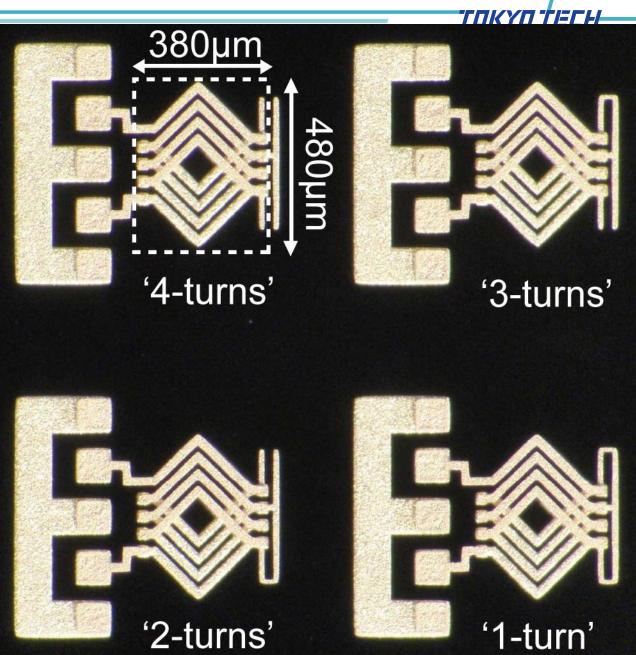

## **Fabricated test inductors**

MEMS process

- •Metal (Au)

- •Two metal layers

- ●Substrate:1**kΩ · cm**

2-bit control Four test inductors were fabricated

32

## **Measurement results of Q-factor**

34

**Pursuing Excellence**

ΤΟΚΥΟ

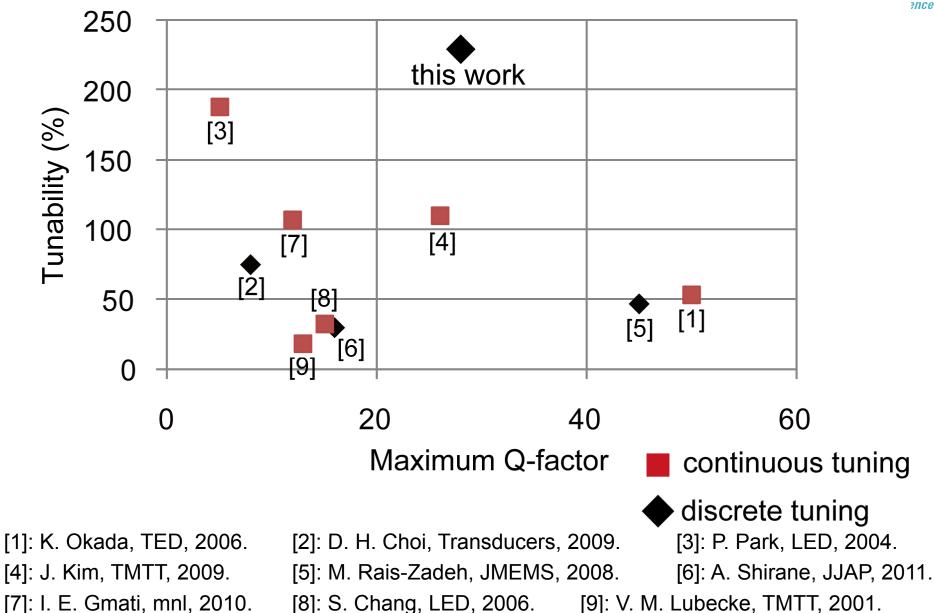

## **Comparison with other works**

nce

ΤΟΚΥΟ

35

- 1. Introduction

- 2. Our RF CMOS development

- Why do we expect heterogeneous integration on CMOS ?

- 3. Our approach to heterogeneous integration: Novel wafer shuttle technique.

- 4. Summary

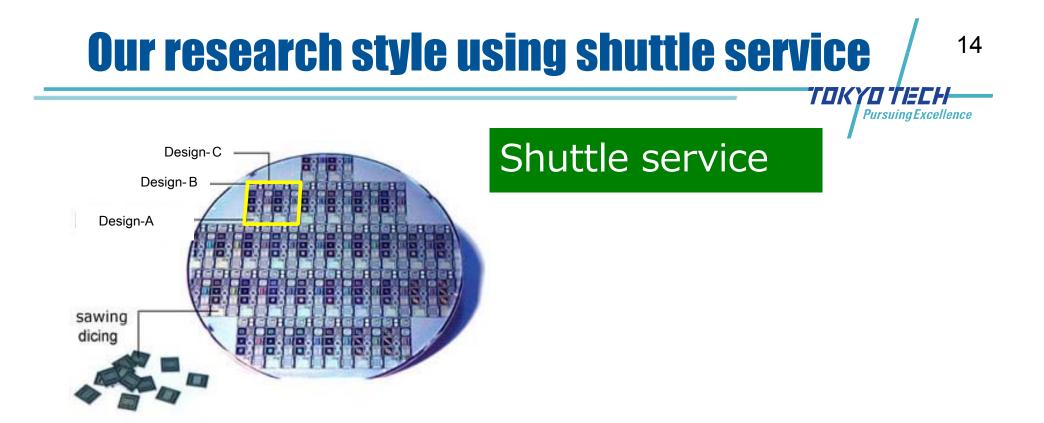

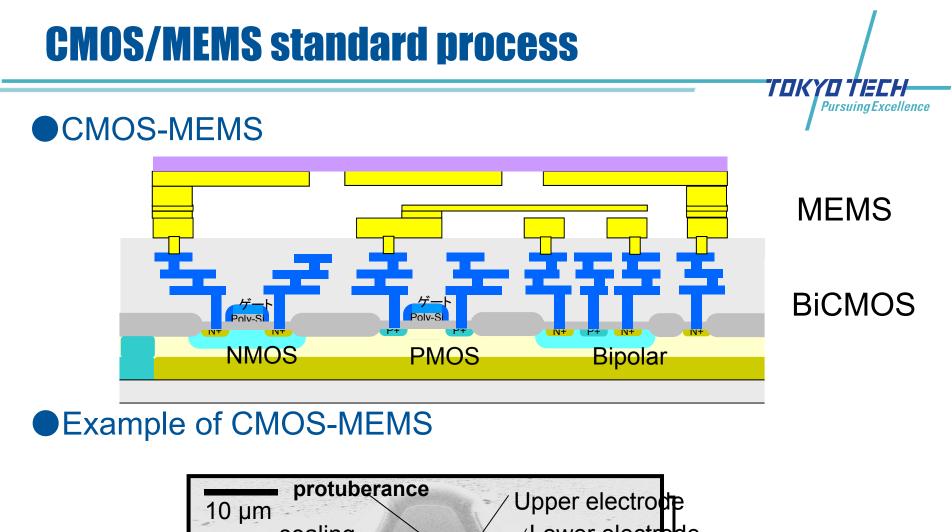

# How to fabricate functionalities on CMOS 37

## Issues

- Do we prepare process equipment?

- If we have process ability, can we fabricate the functionalities on CMOS chip ? Chip sizes are several mm<sup>2</sup>.

- How do we collaborate ? (from the viewpoint of circuit design researcher)

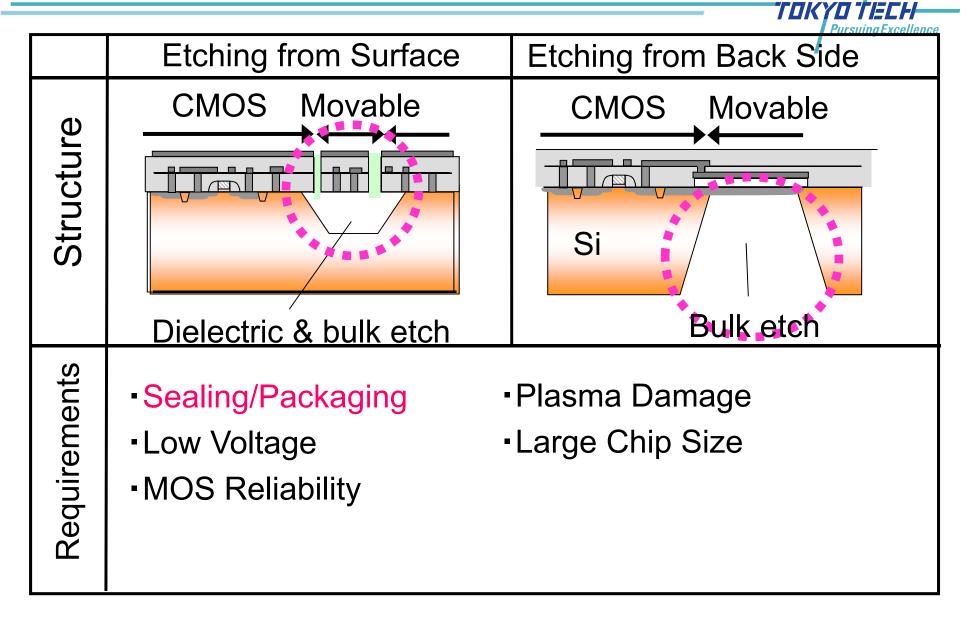

## **Pre-CMOS and Intermediate- CMOS**

Pre- CMOS (MEMS first) **Intermediate- CMOS** CMOS Movable CMOS Movable Structure Si **Poly-Si** Requirements LSI Multilevel Interconnection Sealing/Packaging Large Chip Size Low Voltage

**Pursuina Excellence**

- MOS Reliability Sacrificial Film Etching

- (SiO<sub>2</sub> or SiGe etc.)

## **Post- CMOS** (CMOS-first and MEMS last)

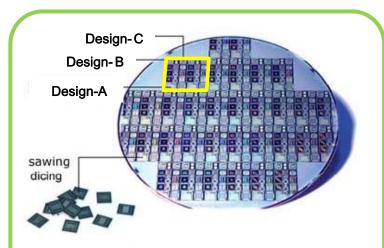

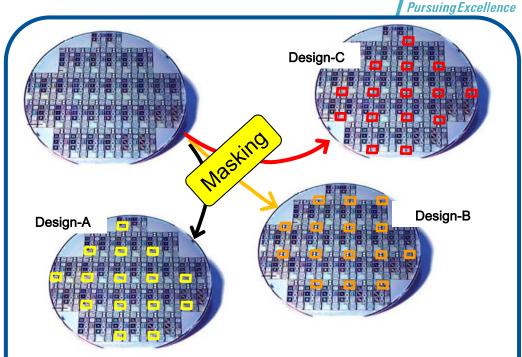

# Toward open collaboration Novel wafer shuttle service for heterogeneous integration

- Designers receive their own circuit as chips.

- Another functions such as sensor, MEMS, photonics etc. cannot be fabricated on the chip.

- So far, CMOS processed wafer cannot be provided because another designer's area cannot be masked.

#### **Conventional shuttle service**

- With novel masking technique, wafers can be provided to each designer. In wafer-A, another designer's area are masked.

- Sensor, MEMS, and photonics can be fabricated or implemented on CMOS wafers!

The novel wafer shuttle has been developed by Tokyo Tech/NTT-AT collaboration.

- MEMS(functionalities)-first is suitable for mass-production type device such as acceleration sensor, pressure sensor, DMD, etc. cf. DRAM, Flash, MPU

- Post process can open the door to various field researchers: circuit, process, bio engineers.

- New wafer shuttle technology

## **Detail of wafer shuttle**

- 0.35µm standard CMOS with 20-V MOSFET, 6 inch wafer

- Area designed by another designer is completely masking by the blind process.

- Design and process integration consulting is available thru Tokyo Tech. Standard MEMS is also available.

- PDK is distributed thru VDEC, Univ. Tokyo

sealing space Si基板 CMOSLSI

Integrated finger print sensor.

Photo: Courtesy of NTT Micro integration Lab.

## **First wafer shuttle**

ΤΟΚΥΟ ΤΙΕΕΗ

### Contributors

- More than 5 universities

- More than 3 research group in Tokyo Tech.

#### • Fields

- Photonics

- MEMS

- RF MEMS

- Sensors (bio, Hall effect)

- Tape out in Sept, 2011. Wafer will be delivered in Dec. 2011

- Circuit designer provided IPs.

## Summary

TOKYD TECH PursuingExcellence

## • RF CMOS developments:

- Scalable RF CMOS using miniaturized CMOS

- Use of functionalities such as RF MEMS inductor

- Wafer shuttle technology

- First wafer will be delivered in Dec. 2011.

- Fundamental circuit IPs will be handle by ICE cube center, Tokyo Tech. These IPs will helpful for collaboration of different field researchers.